博文

未来计算的研究

|||

姜咏江

昨日去参加YOCSOEF的“未来计算”报告会,讲者万里兮和刘东的演讲都很精彩。万老师的系统封装内容非常专业,对我这个外行人来说受益匪浅。刘东博士讲他所领导的Intel公司实验室,用“CPU+FPGA+RL”模式进行计算的研究。

“未来计算”一定是“软硬件一体化”方式,这大概已是人们共识的事情。随着计算机应用的广泛深入,对计算机的可计算品质要求越来越高,特别是对计算速度的需求,绝非是软件方式单独优化所能够办得到的。由于器件物理特性的限制,单一靠计算器件来实现更高速度的计算,同样也是不可能的。因而设计更多的同构或者异构的多元实体,依靠“大兵团”作战,已经成为了“未来计算”的必然趋势。“大兵团”作战关键在于调度。

我很欣赏“刘东的第一定律”,意思是“能作的越多,不能作的也越多”。由这个定律会推论出计算的发展,一定会走向“同构/异构”的多元化格局。“刘东第二定律”说的是“可重构计算应用会越来越多”。出于探讨,我给他加上了“不能完全替代固定计算”。

我之所以要这样说是因为“可重构计算”和“固定多体计算”是追求目标完全不同的两个东西。可重构计算追求的是功能上的替代方式,目标是“变形金刚”式的多功能实现手段,而尽可能地少硬件资源的使用。固定多体计算追求在硬件资源充分的情况下,如何更好地利用硬件资源,发挥“大兵团”作战的优势,加快任务的完成。因而我给他补充了一句话,只是个人见解。

虽然“可重构计算”和“固定多体计算”是两个方面的问题,但它们都是“未来计算”不可缺少的内容。这两种结构方式主要反映的是未来计算硬件方面的需求。在计算中,对于“可重构计算”来说,要解决计算过程中是“全局重构”还是“局部重构”的问题,同时还要探讨“重构机制”给系统运行带来的影响,特别是速度、可靠性和安全性的影响。依靠可编程器件实现的可重构计算主要是“求变”,这对硬件资源有限的时候,会成为计算的有效改善手段,但在功能提升的同时,会牺牲一定的速度。

在硬件资源充分的情况下,固定的硬件结构设计,可以实现多元的同构/异构计算单元,如果能够合理地分配任务,调动全部计算单元工作,那么就能有效地提高整体计算的速度与效率。

肯据莫尔定律,未来硬件资源是会更充足的,因而“固定多体计算”应该成为一定时期未来计算的主要研究形式。

目前,计算机“固定多体计算”的焦点是如何“充分调度”所有的资源,进而加快计算速度。实行的基本方式有两种。一是用已经实现多年的软件调度方式,即用操作系统或协议方式调度管理。二是充分利用逻辑电路的优势,实现高层次统一的“硬逻辑”调度管理。前者不需要在硬件层次上提出更高的要求,因而首先出现了“同构多核”。这种同构多核,只是将多个结构相同的计算机核有效地连接起来,任务就基本完成了,而将核的调度管理任务交给了软件。这种做法的典型就是片上网络结构。

片上网络的优势是能够快速利用原有的软件技术实现商业化。实际上,各种高效的宣传,只是一种泡沫。据网上消息,美国某实验室经过测试得出结论:8核以上的计算机处理器,实际效率不但不升,反而下降。不论这个消息是否可靠,从理论上进行分析,所谓的片上多核,前途堪忧。原因是片上结构具有非片上结构不具备的特性,最重要的是空间的“紧致性”和时间的一致性。这种特征会为数据“同步传输”带来方便。另外,片上结构容易实现“动态结构转换”,从而使器件的逻辑构成能“浑然一体”变化,这更有利于加快数据的整体传输。这种结构“浑然一体”变化,并不是“可重构计算”的变化,而是固定硬件结构的线路通断变化而已。这种线路变化完全可以用高层次的逻辑来进行控制。

高层次的逻辑控制又可以发自执行中的程序需求,从而通过软件来直接对硬件进行逻辑重组,达到“软硬件一体化”的“未来计算”效果。这种结构中程序数据可以实现“整体转换”,这是软件管理方式中线路数据传输方式所无法比拟的。因而单纯地将网络结构移植到片上是不科学的做法。事实将会证明“现代操作系统”处理机管理和内存管理功能,必将淡然退出片上多处理器架构的管理层。

从“刘东第一定律”可以推出计算机处理器“异构多元”是必然的,因而未来运行在多处理器计算机上的程序,由于完成不同局部任务的需要,会频繁地在不同类型的处理器间转换,于是程序数据的线路传输方式转移将会带来巨大的时间消耗。而采用动态的“线路切换”方式来实现程序转移,无疑会收到类似飞机“从螺旋桨到喷气式”改变的效果。

由此看来,未来计算的方式必然要以“动态计算机核心”为主要固定结构框架。要实现动态计算机核心结构框架,必须将内存进行拆分,必须采用“分散式存储结构”。这种分散式存储结构也就瓦解了当前困扰人们的“存储墙”问题。分散存储结构并不需要过多的带宽。从理论上分析,访存带宽的强大需求主要是由于存储器容量过大造成的,这种现象在任何材质的存储器访问上都会产生,原因是访存时间会与存储容量成正比。

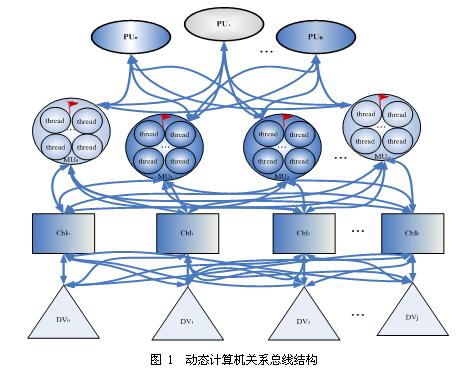

利用万里兮博士的“系统级封装技术”,完全可以做到高性能计算机的微型化。作为动态多处理器计算机,完全可以用“内部动态关系总线”通过高层次的逻辑控制,实现各种资源的有效、高效的分配管理和运用,有效缓解各种传输瓶颈(见图1)。

我的结论是“未来计算”一定是“软硬件一体化”的计算,在片上多处理器结构之下,动态计算机核心一定会成为“高性能适用计算机”的主流产品。

给各位同行一个动态计算机结构的图,除去三角形表示的外设,可以考虑全部结构封装。这种结构几乎可以用在任何的计算机类型中。对于图,配有一定的解释,希望能与同行们一起讨论。

2010-1-9

【附】

如图1所示, PU是单端连接的一类程序执行单位,它只连接MU(包括程序执行环境);Chl是一类双端连接的执行单位,Chl的一端要连接MU,另一端和外设DV连接。每个不同类器件之间,都用总线连接,其中包括控制总线。这些总线都有可控开关控制通断。如果原来的两条或两条以上的总线相连,那么就组成了一条总线(见图2),也就是说不论何种情况,各设备都只能在成为一条的总线上传输数据,而不能同时占用相互冲突的多条总线工作。这种总线结构,我们称之为“动态关系总线”。

动态计算机中这种动态关系总线,形似交叉开关,但实际上是计算机的“核重组”,因为与数据传输中的交叉开关线路结构有本质的不同。不论是单端连接的程序执行单位还是双端连接的程序执行单位,都有自己的指令系统,它们都必需与MU连接才能够执行程序。这种处理器与MU连接之后才会形成能够执行程序的核,我们称之为“执行核”。动态计算机中,同时可以形成许多执行核,执行核还会随着程序执行的需要,在不断地进行着核重组。

MU与单端处理器连接时,其他与MU连接的总线都会处于断开状态。当MU与双端连接处理器Chl的总线连接时,双端连接处理器Chl必须能够找到合适的外设,并与之连接,形成统一的总线结构(见图2),不然就要断开与MU连接的所有总线。这样做的好处是设备不会在连接的状态下不工作,从而保证不出现死锁。

https://blog.sciencenet.cn/blog-340399-285559.html

上一篇:CPU设计我要让更多的人掌握它(续5)

下一篇:CMP的根本出路