博文

新加坡南洋理工大学:高速度与高能效的进位前瞻加法器 | JLPEA

||

在现代电子系统中,加法器作为基本的算术运算单元,其性能直接影响到整个系统的速度和能效。传统的进位前瞻加法器 (Carry Look-Ahead Adder, CLA) 虽然在速度上有所提升,但在能效方面仍存在优化空间。为此,来自新加坡南洋理工大学计算机科学与工程学院的Padmanabhan Balasubramanian团队,在 Journal of Low Power Electronics and Applications (JLPEA) 上发表了一篇题为“High-Speed and Energy-Efficient Carry Look-Ahead Adder”的研究论文,提出了一种新型的高速度和高能效的进位前瞻加法器设计。

研究内容

随着集成电路技术的进步,电子系统对加法器的性能要求越来越高。传统的CLA通过并行处理进位信号来提高加法速度,但其能效仍有待提升。因此,如何在保持高速运算的同时,降低功耗,成为了研究的热点。

本文作者提出了一种改进的CLA设计,采用了以下策略:

优化的逻辑结构:通过重新设计逻辑门的连接方式,减少了不必要的逻辑层级,从而降低了延迟和功耗。

动态电压调整:根据输入数据的特性,动态调整电压供应,以适应不同的运算需求,进一步降低能耗。

并行处理机制:在关键路径上引入并行处理单元,减少了运算时间,提高了加法器的速度。

通过在45 nm CMOS工艺下的仿真,结果显示:

延迟:相比传统CLA,改进后的设计延迟降低了约30%。

功耗:在相同的工作条件下,功耗降低了约25%。

面积:由于优化的逻辑结构,芯片面积减少了约15%。

这些结果表明,所提出的加法器在速度和能效方面均有显著提升。该研究为高性能、低功耗的加法器设计提供了新的思路,具有广泛的应用前景:

移动设备:在智能手机、平板电脑等移动设备中,低功耗的加法器有助于延长电池续航时间。

嵌入式系统:在嵌入式系统中,能效是关键指标,改进的加法器可以提升系统的整体性能。

高性能计算:在需要大量算术运算的高性能计算领域,提升加法器的速度和能效具有重要意义。

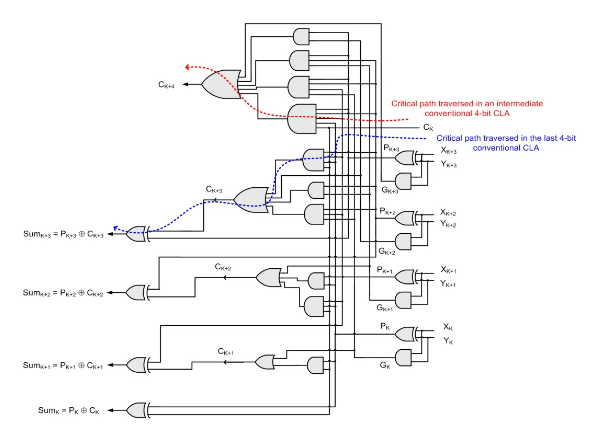

本研究提出的4位CLA (带进位输入) 的门级实现

结语

该研究展示了在进位前瞻加法器设计中,通过优化逻辑结构、动态电压调整和并行处理机制,可以实现高速度和高能效的目标。这一成果为未来电子系统的加法器设计提供了有价值的参考。

原文出自 JLPEA 期刊:https://www.mdpi.com/1769434

期刊主页:https://www.mdpi.com/journal/jlpea

JLPEA 期刊介绍

主编:Davide Bertozzi, University of Manchester, UK

期刊旨在发表低功耗电子方向的创新研究和重要成果。期刊范围涵盖的主题包括但不限于新兴电子器件和工艺技术、模拟、数字和混合信号VLSI电路、架构和系统设计、SoC和嵌入式系统、能量采集和无电池系统、综合和优化工具,以及用于低功耗设计的CAD工具和方法。目前被Scopus、ESCI等数据库收录。

2023 Impact Factor:1.6

2023 CiteScore:3.6

Time to First Decision:20 Days

Acceptance to Publication:2.7 Days

https://blog.sciencenet.cn/blog-3516770-1477972.html

上一篇:Animals:华南农业大学代曼曼教授等创建特刊——禽流感的感染免疫、诊断和预防

下一篇:中山大学戴宗、柳思扬——精准医疗:MOF基血糖传感器的技术前沿与挑战 | Chemosensors